반도체 미세공정의 한계와 칩렛 아키텍처의 부상

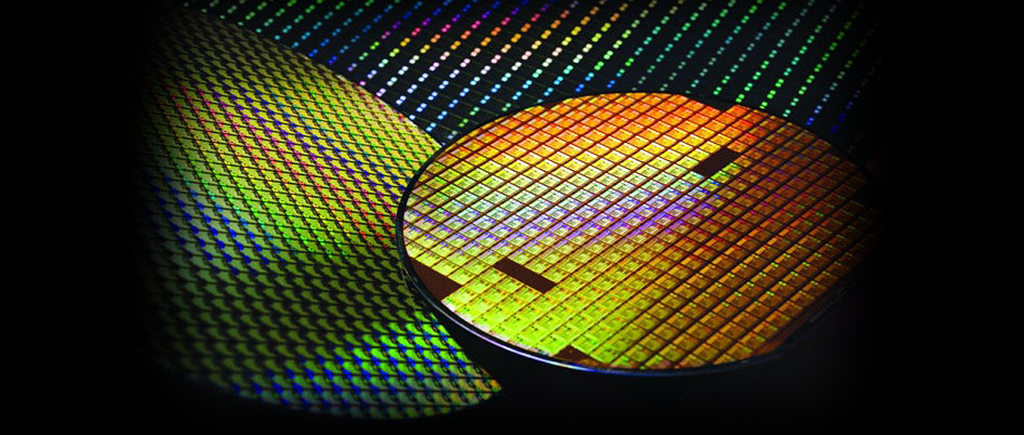

PC 하드웨어의 발전은 언제나 더 작고 정밀한 실리콘 웨이퍼 위에서 이루어졌습니다. 하지만 회로 선폭이 나노미터(nm) 단위의 극한으로 좁아지면서, 하나의 거대한 칩에 모든 기능을 집적하는 전통적인 제조 방식은 막대한 수율 저하와 원가 상승이라는 거대한 벽에 부딪혔습니다.

거대 단일 칩의 종말과 레고 블록의 등장

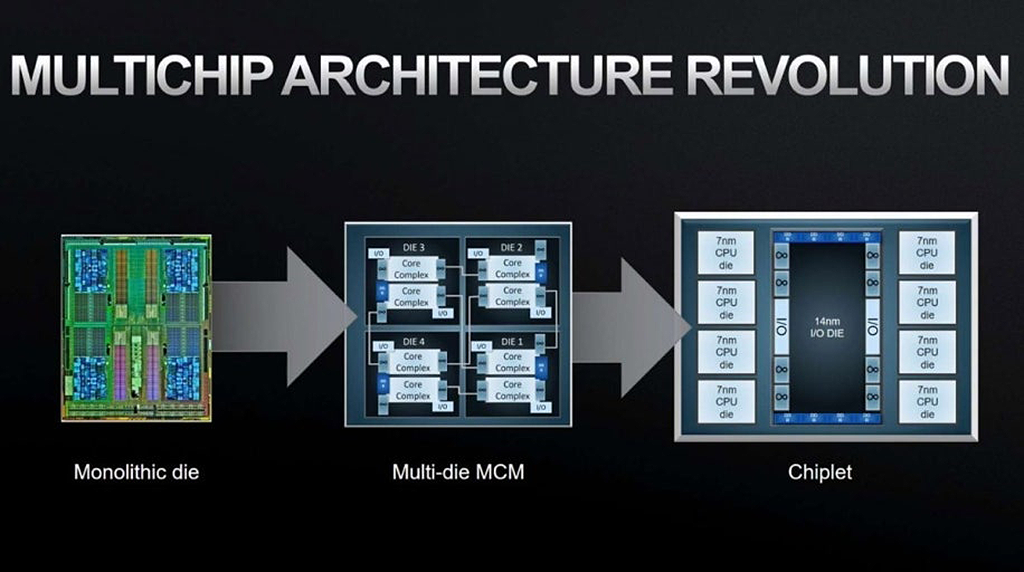

과거에는 CPU 코어, 메모리 컨트롤러, 입출력 단자 등 모든 요소를 하나의 실리콘 덩어리로 구워내는 모놀리식(Monolithic) 방식을 고수했습니다. 반도체 공학 저널인 IEEE Spectrum의 기술 동향 보고서에서 지적하듯, 칩의 면적이 커질수록 웨이퍼 상의 미세한 결함 하나가 전체 칩을 폐기하게 만드는 치명적인 리스크로 작용하게 됩니다.

이러한 수율의 한계를 극복하기 위해 등장한 것이 바로 칩렛(Chiplet) 기술입니다. 마치 레고 블록을 조립하듯, 서로 다른 공정에서 생산된 최적의 소형 칩들을 모아 하나의 기판 위에 이어 붙이는 혁신적인 발상의 전환입니다.

3D 패키징: 평면을 넘어 수직으로 쌓아 올리다

단순히 칩을 평면으로 나열하는 것을 넘어, 최근에는 실리콘 다이를 수직으로 쌓아 올리는 3D 패키징 기술이 하드웨어 업계의 핵심 경쟁력으로 떠올랐습니다. AMD의 3D V-Cache 기술이나 최신 GPU에 적용되는 TSMC의 최첨단 패키징 공정이 대표적인 사례입니다.

- 데이터 병목 해소: 연산 코어와 캐시 메모리를 수직으로 밀착시켜 물리적 거리를 극한으로 줄임으로써, 데이터 전송 속도를 비약적으로 높이고 전력 소모를 통제합니다.

- 제조 공정의 분업화: 핵심 연산 코어는 최신 미세 공정으로, 단순한 입출력 단자는 저렴한 구형 공정으로 각각 분리 생산하여 칩셋 전체의 제조 원가를 기하급수적으로 낮출 수 있습니다.

소비자 가격에 미치는 실질적인 파급력

결과적으로 칩렛과 3D 패키징 기술은 최신 하드웨어의 가격 폭등을 억제하는 가장 강력한 방어선 역할을 수행하고 있습니다. 만약 현재의 16코어, 24코어 하이엔드 데스크탑 프로세서들을 과거의 단일 칩 방식으로 제조했다면, 우리는 지금보다 수배 이상의 비용을 지불해야만 했을 것입니다.

미세공정 전환에 드는 천문학적인 개발 비용을 고려할 때, 칩렛 구조는 제조사와 소비자 모두에게 선택이 아닌 필수 생존 전략이 되었습니다. 우리가 비교적 합리적인 가격에 점점 더 강력해지는 멀티코어 성능을 누릴 수 있는 배경에는, 보이지 않는 패키징 기술의 눈부신 혁신이 굳건히 자리 잡고 있습니다.

'하드웨어' 카테고리의 다른 글

| 심리적 방어선을 뚫어버린 GPU 가격 폭등의 원인과 생존 전략 (0) | 2026.03.20 |

|---|---|

| RTX 50 vs 40 시리즈 가성비 결산 GDDR7과 DLSS 4가 바꾸어 놓은 선택 기준 (0) | 2026.03.19 |

| 메인스트림의 격돌 라이젠 5 9600X vs 코어 울트라 5 245K 완벽 비교 (0) | 2026.03.18 |